SLWS203-DECEMBER 2007

# 11-BIT, 200 MSPS ADC

# **FEATURES**

- Maximum Sample Rate: 200 MSPS

- 11-Bit Resolution

- No Missing Codes

- Total Power Dissipation 1.23 W

- Internal Sample and Hold

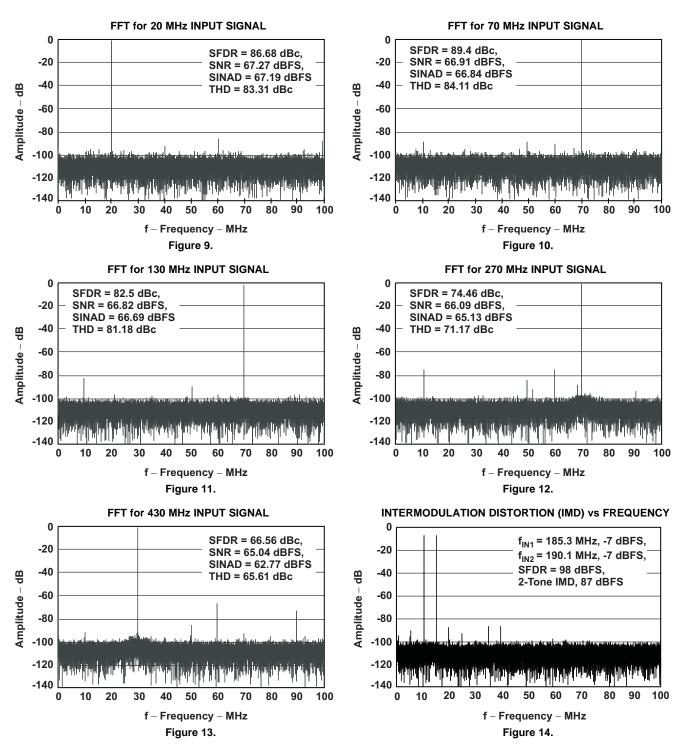

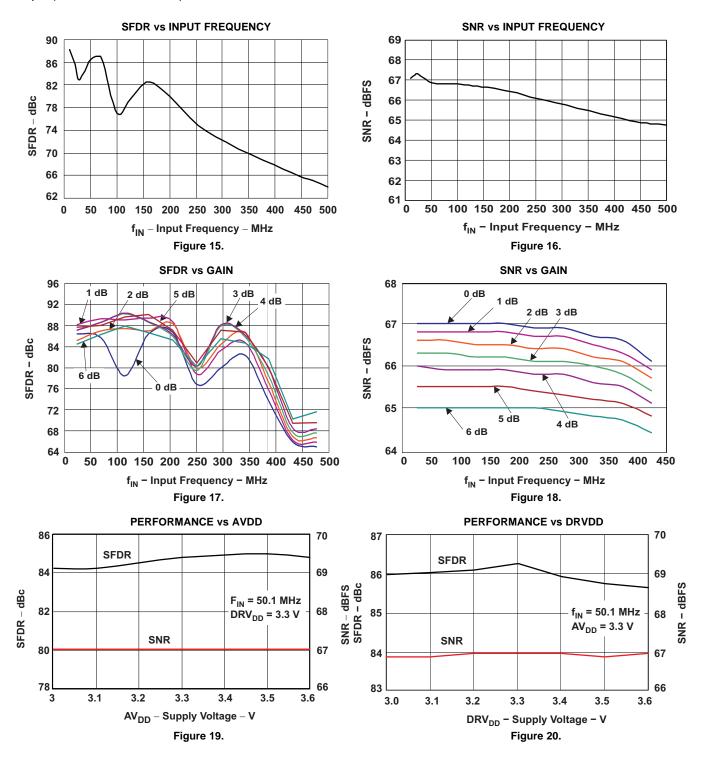

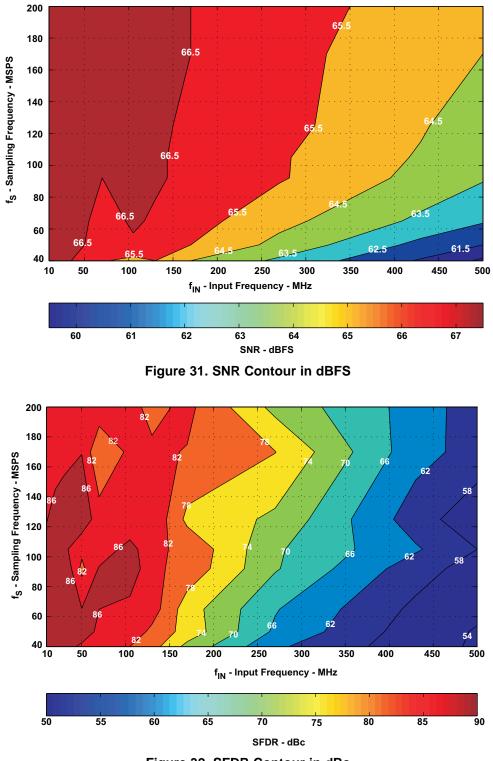

- 67-dBFS SNR at 70-MHz IF

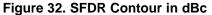

- 84-dBc SFDR at 70-MHz IF, 0-dB Gain

- High Analog Bandwidth up to 800 MHz

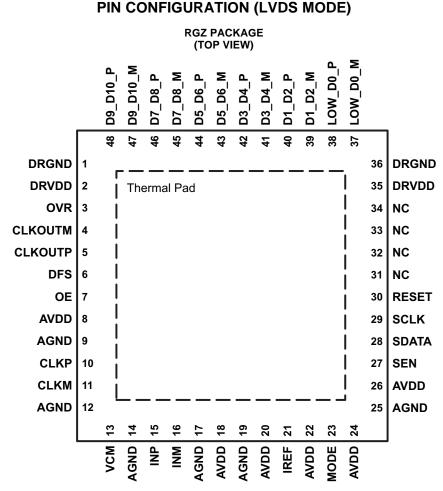

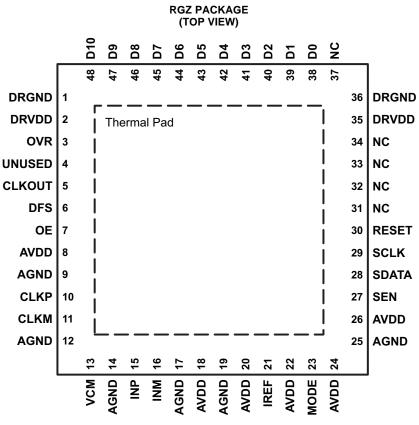

- Double Data Rate (DDR) LVDS and Parallel CMOS Output Options

- Programmable Gain up to 6 dB for SNR/SFDR Trade-Off at High IF

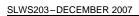

- Reduced Power Modes at Lower Sample Rates

- Supports Input Clock Amplitude Down to 400 mV<sub>PP</sub>

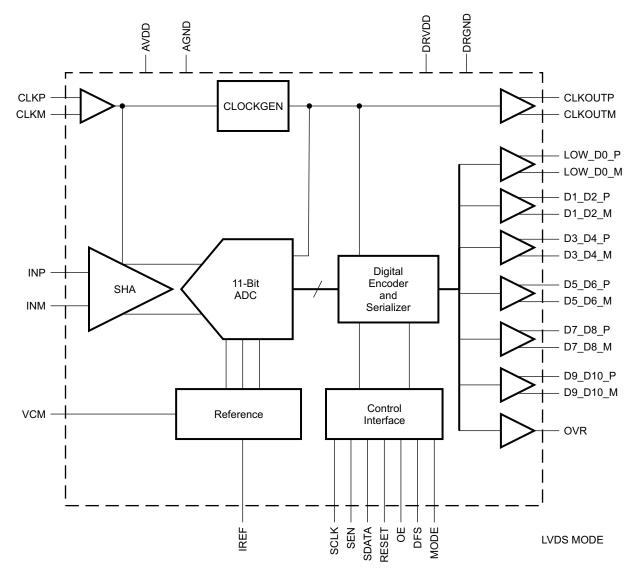

# DESCRIPTION

ADS5517 is a high performance 11-bit, 200-MSPS A/D converter. It offers state-of-the art functionality and performance using advanced techniques to minimize board space. With high analog bandwidth and low jitter input clock buffer, the ADC supports both high SNR and high SFDR at high input frequencies. It features programmable gain options that can be used to improve SFDR performance at lower full-scale analog input ranges.

- Clock Duty Cycle Stabilizer

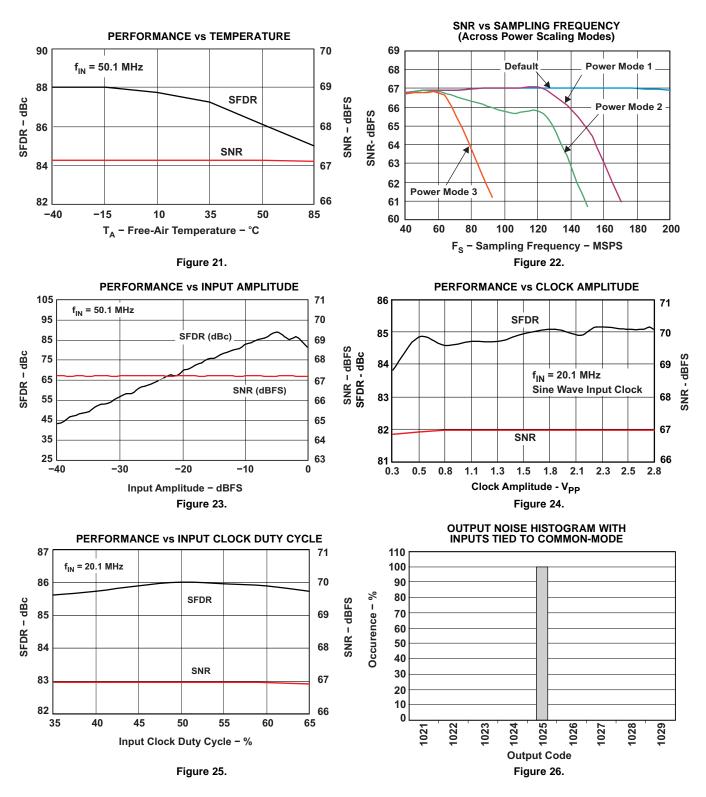

- No External Reference Decoupling Required

- Internal and External Reference Support

- Programmable Output Clock Position to Ease

Data Capture

- 3.3-V Analog and Digital Supply

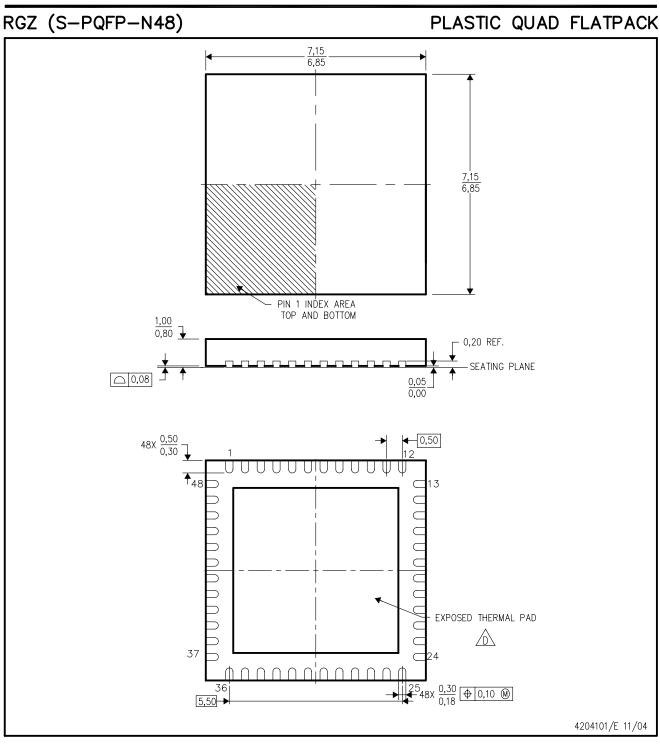

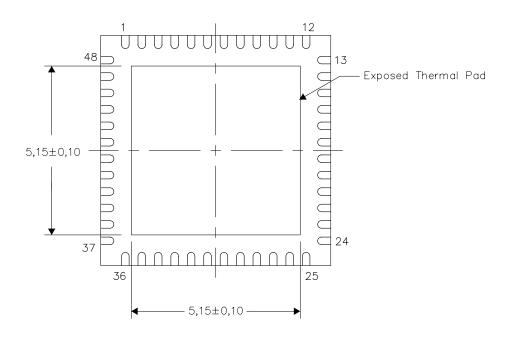

- 48-QFN Package (7 mm × 7 mm)

## APPLICATIONS

- Wireless Communications Infrastructure

- Software Defined Radio

- Power Amplifier Linearization

- 802.16d/e

- Test and Measurement Instrumentation

- High Definition Video

- Medical Imaging

- Radar Systems

In a compact 48-pin QFN, the device offers fully differential LVDS DDR (Double Data Rate) interface while parallel CMOS outputs can also be selected. Flexible output clock position programmability is available to ease capture and trade-off setup for hold times. At lower sampling rates, the ADC can be operated at scaled down power with no loss in performance. The ADS5517 includes an internal reference, while eliminating the traditional reference pins and associated external decoupling. The device also supports an external reference mode.

The device is specified over the industrial temperature range (-40°C to 85°C).

|        | 210 MSPS             | 190 MSPS | 170 MSPS |

|--------|----------------------|----------|----------|

| 14 bit | ADS5547              | ADS5546  | ADS5545  |

| 12 bit | ADS5527              | -        | ADS5525  |

| 11 bit | ADS5517<br>(200MSPS) |          |          |

#### ADS5517 PRODUCT FAMILY

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### SLWS203-DECEMBER 2007

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

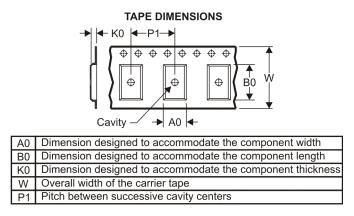

#### PACKAGE/ORDERING INFORMATION<sup>(1)</sup>

| PRODUCT | PACKAGE-<br>LEAD      | PACKAGE<br>DESIGNATOR            | SPECIFIED<br>TEMPERATURE<br>RANGE | TEMPERATURE PACKAGE                            |              | TRANSPORT<br>MEDIA,<br>QUANTITY |

|---------|-----------------------|----------------------------------|-----------------------------------|------------------------------------------------|--------------|---------------------------------|

| ADS5517 | QFN-48 <sup>(2)</sup> | RG7                              | 40°C to 95°C                      | A 76547                                        | ADS5517IRGZT | Tape and Reel,<br>250           |

| AD55517 | QFN-40 <sup>17</sup>  | <sup>(2)</sup> RGZ –40°C to 85°C |                                   | QFN-48 <sup>(2)</sup> RGZ -40°C to 85°C AZ5517 | ADS5517IRGZR | Tape and Reel,<br>2500          |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

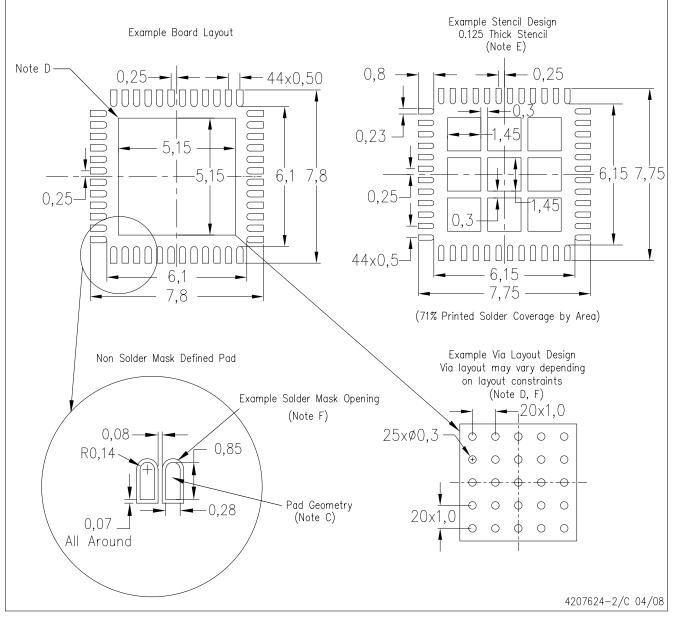

(2) For thermal pad size on the package, see the mechanical drawings at the end of this data sheet. θ<sub>JA</sub> = 25.41°C/W (0 LFM air flow), θ<sub>JC</sub> = 16.5°C/W when used with 2 oz. copper trace and pad soldered directly to a JEDEC standard four layer 3 in x 3 in (7.62 cm x 7.62 cm) PCB.

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                  |                                                         | VALUE                             | UNIT |

|------------------|---------------------------------------------------------|-----------------------------------|------|

|                  | Supply voltage range, AVDD                              | -0.3 to 3.9                       | V    |

|                  | Supply voltage range, DRVDD                             | -0.3 to 3.9                       | V    |

|                  | Voltage between AGND and DRGND                          | -0.3 to 0.3                       | V    |

|                  | Voltage between AVDD to DRVDD                           | -0.3 to 3.3                       | V    |

|                  | Voltage applied to VCM pin (in external reference mode) | -0.3 to 1.8                       | V    |

|                  | Voltage applied to analog input pins, INP and INM       | -0.3 to minimum (3.6, AVDD + 0.3) | V    |

|                  | Voltage applied to input clock pins, CLKP and CLKM      | -0.3 to AVDD + 0.3                | V    |

| T <sub>A</sub>   | Operating free-air temperature range                    | -40 to 85                         | °C   |

| TJ               | Operating junction temperature range                    | 125                               | °C   |

| T <sub>stg</sub> | Storage temperature range                               | -65 to 150                        | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

## **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|       |                                                                                 | MIN         | ТҮР      | MAX  | UNIT            |

|-------|---------------------------------------------------------------------------------|-------------|----------|------|-----------------|

| SUP   | PLIES                                                                           |             |          |      |                 |

|       | Analog supply voltage, AVDD                                                     | 3           | 3.3      | 3.6  | V               |

|       | Digital supply voltage, DRVDD                                                   | 3           | 3.3      | 3.6  | V               |

| ANA   | LOG INPUTS                                                                      |             |          |      |                 |

|       | Differential input voltage range                                                |             | 2        |      | V <sub>PP</sub> |

|       | Input common-mode voltage                                                       |             | 1.5 ±0.1 |      | V               |

|       | Voltage applied on VCM in external reference mode                               | 1.45        | 1.5      | 1.55 | V               |

| CLO   | CK INPUT                                                                        |             |          |      |                 |

|       | Input clock sample rate (1)                                                     |             |          |      | MSPS            |

|       | DEFAULT SPEED mode                                                              | 50          |          | 200  | MSPS            |

|       | LOW SPEED mode                                                                  | 1           |          | 60   | M252            |

|       | Input clock amplitude differential (V <sub>(CLKP)</sub> - V <sub>(CLKM)</sub> ) |             |          |      |                 |

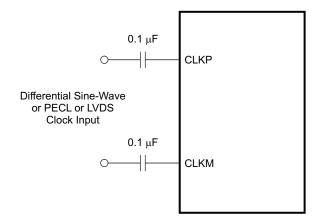

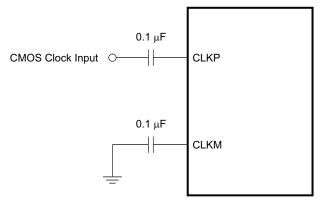

|       | Sine wave, ac-coupled                                                           | 0.4         | 1.5      |      | V <sub>PP</sub> |

|       | LVPECL, ac-coupled                                                              |             | 1.6      |      | V <sub>PP</sub> |

|       | LVDS, ac-coupled                                                                |             | 0.7      |      | V <sub>PP</sub> |

|       | LVCMOS, single-ended, ac-coupled                                                |             | 3.3      |      | V               |

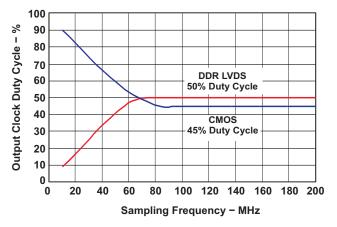

|       | Input clock duty cycle (See Figure 25)                                          | 35%         | 50%      | 65%  |                 |

| DIGI  | TAL OUTPUTS                                                                     |             |          |      |                 |

| $C_L$ | Maximum external load capacitance from each output pin to DRGND (LVDS and CM    | /IOS modes) |          |      |                 |

|       | Without internal termination (default after reset)                              |             | 5        |      | pF              |

|       | With 100 $\Omega$ internal termination <sup>(2)</sup>                           |             | 10       |      | pF              |

| $R_L$ | Differential load resistance between the LVDS output pairs (LVDS mode)          |             | 100      |      | Ω               |

|       | Operating free-air temperature                                                  | -40         |          | 85   | °C              |

(1) See the section on *Low Sampling Frequency Operation* for more information.

(2) See the section on LVDS Buffer Internal termination for more information.

# **ELECTRICAL CHARACTERISTICS**

Typical values are at 25°C, min and max values are across the full temperature range  $T_{MIN} = -40^{\circ}C$  to  $T_{MAX} = 85^{\circ}C$ , AVDD = DRVDD = 3.3 V, sampling rate = 200 MSPS, sine wave input clock, 1.5 V<sub>PP</sub> differential clock amplitude, 50% clock duty cycle, -1 dBFS differential analog input, internal reference mode, 0-db gain, DDR LVDS data output (unless otherwise noted)

|                     | PARAMETER                                                    | TEST CONDITIONS                                                  | MIN  | ТҮР       | MAX | UNIT            |

|---------------------|--------------------------------------------------------------|------------------------------------------------------------------|------|-----------|-----|-----------------|

| Resolution          | 1                                                            |                                                                  |      | 11        |     | bits            |

| ANALOG              | INPUT                                                        |                                                                  |      |           |     |                 |

|                     | Differential input voltage range                             |                                                                  |      | 2         |     | V <sub>PP</sub> |

|                     | Differential input capacitance                               |                                                                  |      | 7         |     | pF              |

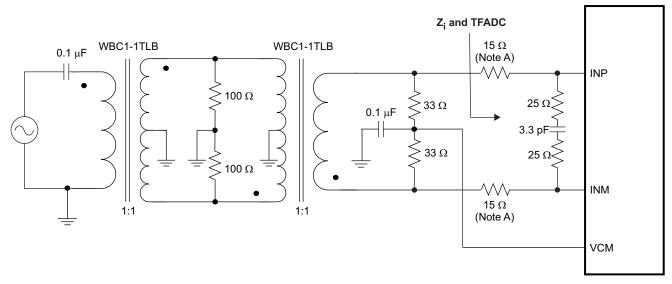

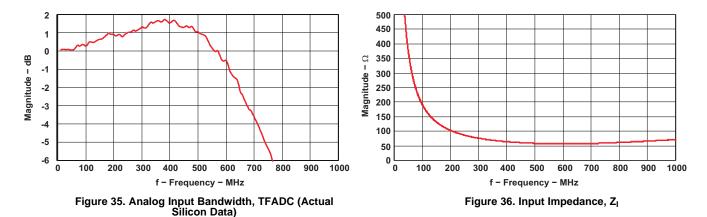

|                     | Analog input bandwidth                                       |                                                                  |      | 800       |     | MHz             |

|                     | Analog input common mode current (per input pin)             |                                                                  |      | 342       |     | μA              |

| REFEREN             | ICE VOLTAGES                                                 |                                                                  |      |           |     |                 |

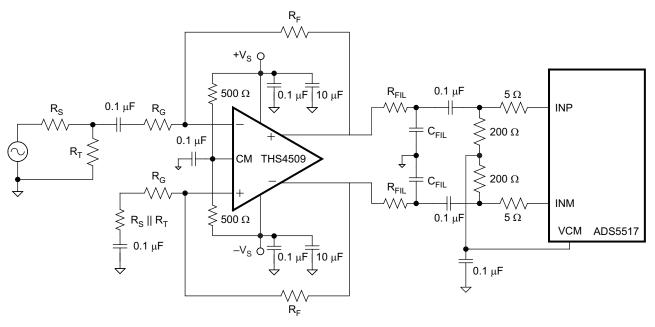

| V <sub>(REFB)</sub> | Internal reference bottom voltage                            | Internal reference mode                                          |      | 0.5       |     | V               |

| V <sub>(REFT)</sub> | Internal reference top voltage                               | Internal reference mode                                          |      | 2.5       |     | V               |

| $\Delta V_{(REF)}$  | Internal reference error                                     | V <sub>(REFT)</sub> - V <sub>(REFB)</sub>                        | -60  | ±25       | 60  | mV              |

| V <sub>CM</sub>     | Common mode output voltage                                   | Internal reference mode                                          |      | 1.5       |     | V               |

|                     | VCM output current capability                                | Internal reference mode                                          |      | ±4        |     | mA              |

| DC ACCU             | RACY                                                         |                                                                  |      |           |     |                 |

|                     | No Missing Codes                                             |                                                                  |      | Specified |     |                 |

| DNL                 | Differential non-linearity                                   |                                                                  | -0.6 | ±0.3      | 1.0 | LSB             |

| INL                 | Integral non-linearity                                       |                                                                  | -1.5 | ±0.6      | 1.5 | LSB             |

|                     | Offset error                                                 |                                                                  | -10  | 5         | 10  | mV              |

|                     | Offset temperature coefficient                               |                                                                  |      | 0.002     |     | ppm/°C          |

|                     | Gain error due to internal reference error alone             | (ΔV <sub>(REF)</sub> / 2.0V)%                                    | -3   | ±1        | 3   | %FS             |

|                     | Gain error excluding internal reference error <sup>(1)</sup> |                                                                  | -2   | ± 1       | 2   | %FS             |

|                     | Gain temperature coefficient                                 |                                                                  |      | 0.01      |     | ∆%/°C           |

| PSRR                | DC Power supply rejection ratio                              |                                                                  |      | 0.6       |     | mV/V            |

| POWER S             | SUPPLY                                                       |                                                                  |      |           |     |                 |

| I <sub>(AVDD)</sub> | Analog supply current                                        |                                                                  |      | 306       |     | mA              |

|                     | Divited and a                                                | LVDS mode, $I_O = 3.5$ mA, $R_L = 100 \ \Omega$ , $C_L = 5 \ pF$ |      | 66        |     | mA              |

| (DRVDD)             | Digital supply current                                       | CMOS mode, $F_{IN}$ = 2.5 MHz, $C_L$ = 5 pF                      |      | 47        |     | mA              |

| I <sub>CC</sub>     | Total supply current                                         | LVDS mode                                                        |      | 372       |     | mA              |

|                     | Total power dissipation                                      | LVDS mode                                                        |      | 1.23      | 1.4 | W               |

|                     | Standby power                                                | In STANDBY mode with clock stopped                               |      | 100       | 150 | mW              |

|                     | Clock stop power                                             | With input clock stopped                                         |      | 100       | 150 | mW              |

(1) Gain error is specified from design and characterization; it is not tested in production.

4

# **ELECTRICAL CHARACTERISTICS**

Typical values are at 25°C, min and max values are across the full temperature range  $T_{MIN} = -40^{\circ}C$  to  $T_{MAX} = 85^{\circ}C$ , AVDD = DRVDD = 3.3 V, sampling rate = 200 MSPS, sine wave input clock, 1.5 V<sub>PP</sub> differential clock amplitude, 50% clock duty cycle, -1 dBFS differential analog input, internal reference mode, 0-db gain, DDR LVDS data output (unless otherwise noted)

|       | PARAMETER                            | TE                            | ST CONDITIONS                                  | MIN  | TYP  | MAX | UNIT  |

|-------|--------------------------------------|-------------------------------|------------------------------------------------|------|------|-----|-------|

| AC CH | ARACTERISTICS                        |                               |                                                | · ·  |      |     |       |

|       |                                      | F <sub>IN</sub> = 20 MHz      |                                                |      | 67.1 |     |       |

|       |                                      | F <sub>IN</sub> = 70 MHz      |                                                | 64.5 | 66.9 |     |       |

|       |                                      | F <sub>IN</sub> = 100 MHz     |                                                |      | 66.8 |     |       |

| CNID  | Signal to paigo ratio                | F <sub>IN</sub> = 170 MHz     |                                                |      | 66.6 |     |       |

| SNR   | Signal to noise ratio                | E 220 MU                      | 0 dB gain, 2 V <sub>PP</sub> FS <sup>(1)</sup> |      | 66   |     | dBFS  |

|       |                                      | $F_{IN} = 230 \text{ MHz}$    | 3 dB gain, 1.4 V <sub>PP</sub> FS              |      | 65.4 |     |       |

|       |                                      | E 400 MU                      | 0 dB gain, 2 V <sub>PP</sub> FS                |      | 65   |     |       |

|       |                                      | $F_{IN} = 400 \text{ MHz}$    | 3 dB gain, 1.4 V <sub>PP</sub> FS              |      | 64.5 |     |       |

|       |                                      | F <sub>IN</sub> = 20 MHz      |                                                |      | 86   |     |       |

|       |                                      | F <sub>IN</sub> = 70 MHz      |                                                | 75   | 84   |     |       |

|       |                                      | $F_{IN} = 100 \text{ MHz}$    |                                                |      | 78   |     |       |

|       |                                      | F <sub>IN</sub> = 170 MHz     |                                                |      | 79   |     |       |

|       | Courieus free dunamie renge          | E 220 MU                      | 0 dB gain, 2 V <sub>PP</sub> FS                |      | 75   |     | dDa   |

| SFDR  | Spurious free dynamic range          | F <sub>IN</sub> = 230 MHz     | 3 dB gain, 1.4 V <sub>PP</sub> FS              |      | 78   |     | dBc   |

|       |                                      | F <sub>IN</sub> = 300 MHz     | 0 dB gain, 2 V <sub>PP</sub> FS                |      | 74   |     |       |

|       |                                      |                               | 3 dB gain, 1.4 V <sub>PP</sub> FS              |      | 76   |     |       |

|       |                                      | F <sub>IN</sub> = 400 MHz     | 0 dB gain, 2 V <sub>PP</sub> FS                |      | 68   |     |       |

|       |                                      |                               | 3 dB gain, 1.4 V <sub>PP</sub> FS              |      | 70   |     |       |

|       |                                      | $F_{IN} = 20 \text{ MHz}$     |                                                |      | 67   |     |       |

|       |                                      | $F_{IN} = 70 \text{ MHz}$     |                                                | 64   | 66.8 |     |       |

|       |                                      | $F_{IN} = 100 \text{ MHz}$    |                                                |      | 66.6 |     |       |

|       | Cignal to paigo and distortion ratio | F <sub>IN</sub> = 170 MHz     |                                                |      | 66.4 |     | dBFS  |

| SINAD | Signal to noise and distortion ratio | E _ 220 MHz                   | 0 dB gain, 2 V <sub>PP</sub> FS                |      | 65   |     | UDF 5 |

|       |                                      | F <sub>IN</sub> = 230 MHz     | 3 dB gain, 1.4 V <sub>PP</sub> FS              |      | 65   |     |       |

|       |                                      | F <sub>IN</sub> = 400 MHz     | 0 dB gain, 2 V <sub>PP</sub> FS                |      | 62.8 |     |       |

|       |                                      | $\Gamma_{\rm IN} = 400$ Wi 12 | 3 dB gain, 1.4 $V_{PP}$ FS                     |      | 62.9 |     |       |

|       |                                      | $F_{IN} = 20 \text{ MHz}$     |                                                |      | 91   |     |       |

|       |                                      | $F_{IN} = 70 \text{ MHz}$     |                                                | 75   | 88   |     |       |

|       |                                      | $F_{IN} = 100 \text{ MHz}$    |                                                |      | 87   |     |       |

|       |                                      | $F_{IN} = 170 \text{ MHz}$    |                                                |      | 87   |     |       |

| HD2   | Second harmonic                      | E 220 M⊔-                     | 0 dB gain, 2 V <sub>PP</sub> FS                |      | 86   |     | dBo   |

| צטרו  |                                      | F <sub>IN</sub> = 230 MHz     | 3 dB gain, 1.4 V <sub>PP</sub> FS              |      | 88   |     | dBc   |

|       |                                      | E _ 200 MU-                   | 0 dB gain, 2 V <sub>PP</sub> FS                |      | 78   |     |       |

|       |                                      | F <sub>IN</sub> = 300 MHz     | 3 dB gain, 1.4 V <sub>PP</sub> FS              |      | 80   |     |       |

|       |                                      |                               | 0 dB gain, 2 V <sub>PP</sub> FS                |      | 69   |     |       |

|       |                                      | $F_{IN} = 400 \text{ MHz}$    | 3 dB gain, 1.4 V <sub>PP</sub> FS              |      | 71   |     |       |

# **ELECTRICAL CHARACTERISTICS (continued)**

Typical values are at 25°C, min and max values are across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, AVDD = DRVDD = 3.3 V, sampling rate = 200 MSPS, sine wave input clock, 1.5 V<sub>PP</sub> differential clock amplitude, 50% clock duty cycle, -1 dBFS differential analog input, internal reference mode, 0-db gain, DDR LVDS data output (unless otherwise noted)

|         | PARAMETER                           | TE                                                                                    | ST CONDITIONS                                                 | MIN  | TYP  | MAX | UNIT            |

|---------|-------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------|------|------|-----|-----------------|

|         |                                     | F <sub>IN</sub> = 20 MHz                                                              |                                                               |      | 86   |     |                 |

|         |                                     | F <sub>IN</sub> = 70 MHz                                                              |                                                               | 75   | 84   |     |                 |

|         |                                     | $F_{IN} = 100 \text{ MHz}$                                                            |                                                               |      | 78   |     |                 |

|         |                                     | F <sub>IN</sub> = 170 MHz                                                             |                                                               |      | 79   |     |                 |

|         | The local decision of the           | E 000 MIL                                                                             | 0 dB gain, 2 V <sub>PP</sub> FS                               |      | 75   |     |                 |

| HD3     | Third harmonic                      | $F_{IN} = 230 \text{ MHz}$                                                            | 3 dB gain, 1.4 V <sub>PP</sub> FS                             |      | 78   |     | dBc             |

|         |                                     | E 200 MU                                                                              | 0 dB gain, 2 V <sub>PP</sub> FS                               |      | 74   |     |                 |

|         |                                     | $F_{IN} = 300 \text{ MHz}$                                                            | 3 dB gain, 1.4 V <sub>PP</sub> FS                             |      | 76   |     |                 |

|         |                                     | E 400 MIL                                                                             | 0 dB gain, 2 V <sub>PP</sub> FS                               |      | 68   |     |                 |

|         |                                     | $F_{IN} = 400 \text{ MHz}$                                                            | 3 dB gain, 1.4 V <sub>PP</sub> FS                             |      | 70   |     |                 |

|         |                                     | F <sub>IN</sub> = 20 MHz                                                              |                                                               |      | 95   |     |                 |

|         |                                     | F <sub>IN</sub> = 70 MHz                                                              |                                                               |      | 92   |     |                 |

|         |                                     | F <sub>IN</sub> = 100 MHz                                                             |                                                               |      | 92   | 92  |                 |

| Worst h | armonic (other than HD2, HD3)       | F <sub>IN</sub> = 170 MHz                                                             |                                                               |      | 90   |     | dBc             |

|         |                                     | F <sub>IN</sub> = 230 MHz                                                             |                                                               |      | 90   |     |                 |

|         |                                     | F <sub>IN</sub> = 300 MHz                                                             |                                                               | 88   |      |     |                 |

|         |                                     | $F_{IN} = 400 \text{ MHz}$                                                            |                                                               | 87   |      |     |                 |

|         |                                     | F <sub>IN</sub> = 20 MHz                                                              |                                                               |      | 83   |     |                 |

|         |                                     | F <sub>IN</sub> = 70 MHz                                                              |                                                               | 73   | 82   |     |                 |

|         |                                     | F <sub>IN</sub> = 100 MHz                                                             |                                                               |      | 76   |     |                 |

| THD     | Total harmonic distortion           | F <sub>IN</sub> = 170 MHz                                                             |                                                               |      | 77   | 7 d |                 |

|         |                                     | F <sub>IN</sub> = 230 MHz                                                             |                                                               |      | 73   |     |                 |

|         |                                     | F <sub>IN</sub> = 300 MHz                                                             |                                                               |      | 72   |     |                 |

|         |                                     | $F_{IN} = 400 \text{ MHz}$                                                            |                                                               |      | 65   |     |                 |

| ENOB    | Effective number of bits            | F <sub>IN</sub> = 70 MHz                                                              |                                                               | 10.3 | 10.8 |     | bits            |

| IMD Two | <b>-</b>                            | $F_{IN1} = 50.03 \text{ MHz}, F_{IN2} = 46.03 \text{ MHz}, -7 \text{ dBFS each tone}$ |                                                               |      | 91   |     | 1050            |

|         | Two-tone intermodulation distortion | F <sub>IN1</sub> = 190.1 MHz<br>-7 dBFS each ton                                      | , F <sub>IN2</sub> = 185.02 MHz,<br>e                         |      | 86   |     | dBFS            |

| PSRR    | AC power supply rejection ratio     | 30 MHz, 200 mV <sub>P</sub>                                                           | P signal on 3.3-V supply                                      |      | 35   |     | dBc             |

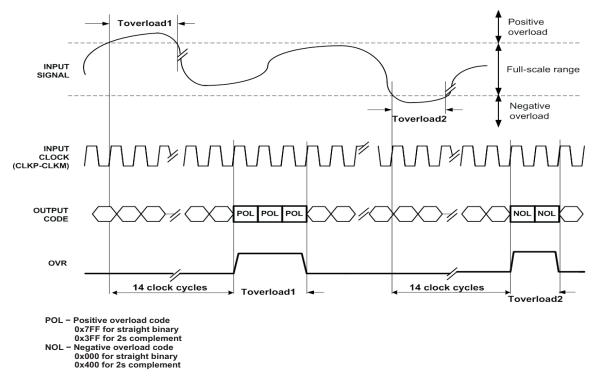

|         | Voltage overload recovery time      |                                                                                       | of final value) for 6-dB overload<br>out at Nyquist frequency |      | 1    |     | Clock<br>cycles |

6

## DIGITAL CHARACTERISTICS<sup>(1)</sup>

The DC specifications refer to the condition where the digital outputs are not switching, but are permanently at a valid logic level 0 or 1 AVDD = DRVDD = 3.3 V,  $I_0$  = 3.5 mA,  $R_L$  = 100  $\Omega$ <sup>(2)</sup>

| PARAMETER                                           | TEST CONDITIONS                                                    | MIN | TYP  | MAX | UNIT |

|-----------------------------------------------------|--------------------------------------------------------------------|-----|------|-----|------|

| DIGITAL INPUTS                                      | -                                                                  |     |      |     |      |

| High-level input voltage                            |                                                                    | 2.4 |      |     | V    |

| Low-level input voltage                             |                                                                    |     |      | 0.8 | V    |

| High-level input current                            |                                                                    |     | 33   |     | μA   |

| Low-level input current                             |                                                                    |     | -33  |     | μA   |

| Input capacitance                                   |                                                                    |     | 4    |     | pF   |

| DIGITAL OUTPUTS – CMOS MODE                         |                                                                    |     |      |     |      |

| High-level output voltage                           |                                                                    |     | 3.3  |     | V    |

| Low-level output voltage                            |                                                                    |     | 0    |     | V    |

| Output capacitance                                  | Output capacitance inside the device, from each output to ground   |     | 2    |     | pF   |

| DIGITAL OUTPUTS – LVDS MODE                         |                                                                    |     |      |     |      |

| High-level output voltage                           |                                                                    |     | 1375 |     | mV   |

| Low-level output voltage                            |                                                                    |     | 1025 |     | mV   |

| Output differential voltage,  V <sub>OD</sub>       |                                                                    | 225 | 350  | 425 | mV   |

| V <sub>OS</sub> Output offset voltage, single-ended | Common-mode voltage of OUTP and OUTM                               |     | 1200 |     | mV   |

| Output capacitance                                  | Output capacitance inside the device, from either output to ground |     | 2    |     | pF   |

(1) All LVDS and CMOS specifications are characterized, but not tested at production.

(2) Io refers to the LVDS buffer current setting, R<sub>L</sub> is the differential load resistance between the LVDS output pair.

## TIMING CHARACTERISTICS – LVDS AND CMOS MODES<sup>(1)</sup>

Typical values are at 25°C, min and max values are across the full temperature range  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = 85^{\circ}$ C, AVDD = DRVDD = 3.3 V, sampling frequency = 200 MSPS, sine wave input clock, 1.5 V<sub>PP</sub> clock amplitude, C<sub>L</sub> = 5 pF<sup>(2)</sup>, I<sub>O</sub> = 3.5 mA, R<sub>L</sub> = 100  $\Omega$ <sup>(3)</sup>, no internal termination, unless otherwise noted.

For timings at lower sampling frequencies, see the *Output Timing* section in the APPLICATION INFORMATION of this data sheet.

|                   | PARAMETER                     | TEST CONDITIONS                                                  | MIN  | TYP | MAX | UNIT            |

|-------------------|-------------------------------|------------------------------------------------------------------|------|-----|-----|-----------------|

| t <sub>a</sub> A  | perture delay                 |                                                                  |      | 1.2 |     | ns              |

| t <sub>j</sub> A  | perture jitter                |                                                                  |      | 150 |     | fs rms          |

| 14                | Voko un timo                  | Time to valid data after coming out of STANDBY mode              |      |     | 100 |                 |

| V                 | Wake-up time                  | Time to valid data after stopping and restarting the input clock |      |     | 100 | μs              |

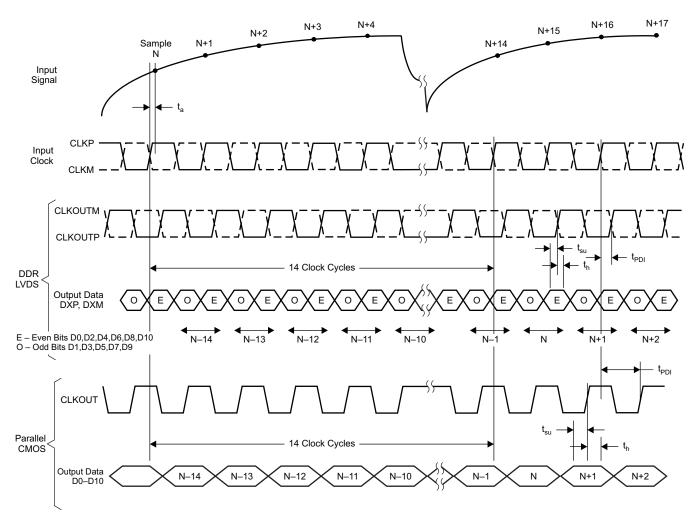

| La                | atency                        |                                                                  |      | 14  |     | clock<br>cycles |

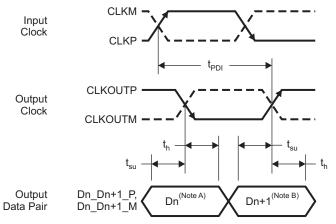

| DDR LVDS I        | MODE <sup>(4)</sup>           | <u>_</u>                                                         |      |     |     |                 |

| t <sub>su</sub> D | ata setup time <sup>(5)</sup> | Data valid <sup>(6)</sup> to zero-cross of CLKOUTP               | 1.0  | 1.5 |     | ns              |

| t <sub>h</sub> D  | Pata hold time <sup>(5)</sup> | Zero-cross of CLKOUTP to data becoming invalid <sup>(6)</sup>    | 0.35 | 0.8 |     | ns              |

(1) Timing parameters are specified by design and characterization and not tested in production.

(2) C<sub>L</sub> is the effective external single-ended load capacitance between each output pin and ground.

(3)  $I_0$  refers to the LVDS buffer current setting;  $R_L$  is the differential load resistance between the LVDS output pair.

(4) Measurements are done with a transmission line of 100 Ω characteristic impedance between the device and the load.

- (5) Setup and hold time specifications take into account the effect of jitter on the output data and clock. These specifications also assume that the data and clock paths are perfectly matched within the receiver. Any mismatch in these paths within the receiver would appear as reduced timing margin.

- (6) Data valid refers to logic high of +50 mV and logic low of -50 mV.

## TIMING CHARACTERISTICS – LVDS AND CMOS MODES (continued)

For timings at lower sampling frequencies, see the Output Timing section in the APPLICATION INFORMATION of this data sheet.

|                                                | PARAMETER                                         | TEST CONDITIONS                                                                                                                       | MIN | TYP | MAX | UNIT  |

|------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| t <sub>PDI</sub>                               | Clock propagation delay <sup>(7)</sup>            | Input clock rising edge zero-cross to output clock rising edge zero-cross                                                             | 3.7 | 4.4 | 5.1 | ns    |

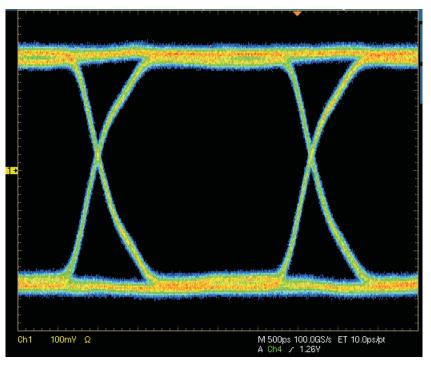

|                                                | LVDS bit clock duty cycle                         | Duty cycle of differential clock,<br>(CLKOUTP-CLKOUTM)<br>80 ≤ Fs ≤ 200 MSPS                                                          | 45% | 50% | 55% |       |

| t <sub>r</sub> ,<br>t <sub>f</sub>             | Data rise time,<br>Data fall time                 | Rise time measured from $-50 \text{ mV}$ to 50 mV<br>Fall time measured from 50 mV to $-50 \text{ mV}$<br>1 $\leq$ Fs $\leq$ 200 MSPS | 50  | 100 | 200 | ps    |

| t <sub>CLKRISE</sub> ,<br>t <sub>CLKFALL</sub> | Output clock rise time,<br>Output clock fall time | Rise time measured from $-50 \text{ mV}$ to 50 mV<br>Fall time measured from 50 mV to $-50 \text{ mV}$<br>1 $\leq$ Fs $\leq$ 200 MSPS | 50  | 100 | 200 | ps    |

|                                                | Output clock jitter                               | Cycle-to-cycle jitter                                                                                                                 |     | 120 |     | ps pp |

| t <sub>OE</sub>                                | Output enable (OE) to valid data delay            | Time to valid data after OE becomes active                                                                                            |     |     | 1   | μs    |

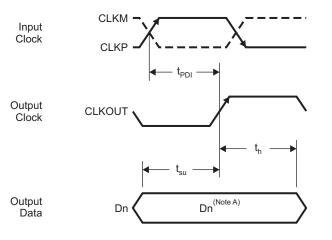

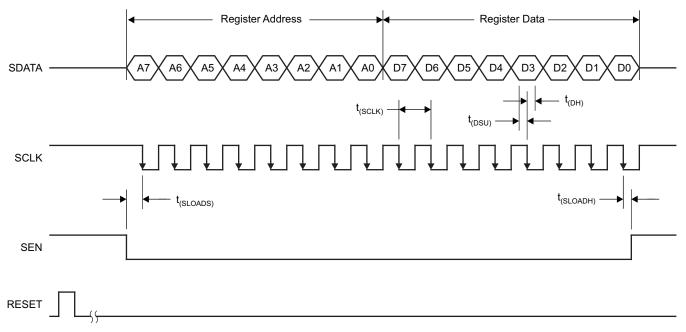

| PARALLI                                        | EL CMOS MODE                                      |                                                                                                                                       |     |     |     |       |

| t <sub>su</sub>                                | Data setup time <sup>(5)</sup>                    | Data valid <sup>(8)</sup> to 50% of CLKOUT rising edge                                                                                | 1.8 | 2.6 |     | ns    |

| t <sub>h</sub>                                 | Data hold time <sup>(5)</sup>                     | 50% of CLKOUT rising edge to data becoming invalid <sup>(8)</sup>                                                                     | 0.4 | 0.8 |     | ns    |

| t <sub>PDI</sub>                               | Clock propagation delay <sup>(7)</sup>            | Input clock rising edge zero-cross to 50% of CLKOUT rising edge                                                                       | 2.6 | 3.4 | 4.2 | ns    |

|                                                | Output clock duty cycle                           | Duty cycle of output clock (CLKOUT)<br>80 ≤ Fs ≤ 200 MSPS                                                                             |     | 45% |     |       |

| t <sub>r</sub> ,<br>t <sub>f</sub>             | Data rise time,<br>Data fall time                 | Rise time measured from 20% to 80% of DRVDD<br>Fall time measured from 80% to 20% of DRVDD<br>$1 \le Fs \le 200 MSPS$                 | 0.8 | 1.5 | 2.0 | ns    |

| t <sub>CLKRISE</sub> ,<br>t <sub>CLKFALL</sub> | Output clock rise time,<br>Output clock fall time | Rise time measured from 20% to 80% of DRVDD<br>Fall time measured from 80% to 20% of DRVDD<br>$1 \le Fs \le 200 MSPS$                 | 0.4 | 0.8 | 1.2 | ns    |

| t <sub>OE</sub>                                | Output enable (OE) to valid data delay            | Time to valid data after OE becomes active                                                                                            |     |     | 50  | ns    |

To use the input clock as the data capture clock, it is necessary to delay the input clock by a delay (t<sub>D</sub>) to get the desired setup and hold (7) times. Use either of these equations to calculate t<sub>D</sub>: Desired setup time =  $t_D - (t_{PDI} - t_{Su})$ Desired hold time =  $(t_{PDI} + t_h) - t_D$ (8) Data valid refers to logic high of 2 V and logic low of 0.8 V

8

Figure 1. Latency

SLWS203-DECEMBER 2007

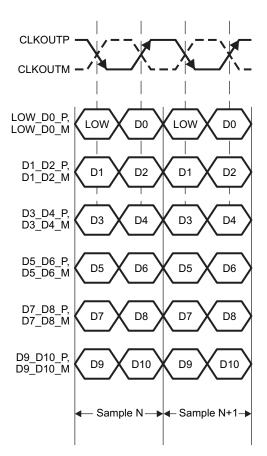

- A. Dn Bits D1, D3, D5, D7, and D9

- B. Dn+1 Bits D0, D2, D4, D6, D8, and D10

Figure 2. LVDS Mode Timing

A. Dn – Bits D0–D10

## **DEVICE PROGRAMMING MODES**

ADS5517 offers flexibility with several programmable features that are easily configured.

The device can be configured independently using either parallel interface control or serial interface programming.

In addition, the device supports a third configuration mode, where both the parallel interface and the serial control registers are used. In this mode, the priority between the parallel and serial interfaces is determined by a priority table (Table 2). If this additional level of flexibility is not required, the user can select either the serial interface programming or the parallel interface control.

## USING PARALLEL INTERFACE CONTROL ONLY

To control the device using parallel interface, keep RESET tied to **high** (DRVDD). Pins DFS, MODE, SEN, SCLK, and SDATA are used to directly control certain modes of the ADC. The device is configured by connecting the parallel pins to the correct voltage levels (as described in Table 3 to Table 7). There is no need to apply reset.

In this mode, SEN, SCLK, and SDATA function as parallel interface control pins. Frequently used functions are controlled in this mode—standby, selection between LVDS/CMOS output format, internal/external reference, two's complement/straight binary output format, and position of the output clock edge.

Table 1 has a description of the modes controlled by the parallel pins.

| PIN   | CONTROL MODES                                                                        |  |  |

|-------|--------------------------------------------------------------------------------------|--|--|

| DFS   | DATA FORMAT and the LVDS/CMOS output interface                                       |  |  |

| MODE  | E Internal or external reference                                                     |  |  |

| SEN   | CLKOUT edge programmability                                                          |  |  |

| SCLK  | LOW SPEED mode control for low sampling frequencies (< 50 MSPS)                      |  |  |

| SDATA | STANDBY mode - Global (ADC, internal references and output buffers are powered down) |  |  |

#### Table 1. Parallel Pin Definition

#### USING SERIAL INTERFACE PROGRAMMING ONLY

To program using the serial interface, the internal registers must first be reset to their default values, and the RESET pin must be kept **low**. In this mode, SEN, SDATA, and SCLK function as serial interface pins and are used to access the internal registers of ADC. The registers are reset either by applying a pulse on the RESET pin, or by a **high** setting on the <RST> bit (D1 in register 0x6C). The *serial interface section* describes the register programming and register reset in more detail.

Since the parallel pins DFS and MODE are not used in this mode, they must be tied to ground.

#### USING BOTH THE SERIAL INTERFACE AND PARALLEL CONTROLS

For increased flexibility, a combination of serial interface registers and parallel pin controls (DFS, MODE) can also be used to configure the device.

The serial registers must first be reset to their default values and the RESET pin must be kept **low**. In this mode, SEN, SDATA, and SCLK function as serial interface pins and are used to access the internal registers of ADC. The registers are reset either by applying a pulse on RESET pin or by a **high** setting on the <RST> bit (D1 in register 0x6C). The *serial interface section* describes the register programming and register reset in more detail.

The parallel interface control pins DFS and MODE are used and their function is determined by the appropriate voltage levels as described in Table 6 and Table 7. The voltage levels are derived by using a resistor string as illustrated in Figure 4. Since some functions are controlled using both the parallel pins and serial registers, the priority between the two is determined by a priority table (Table 2).

|                                                                                                                                                                            | Table 2. I nonty between raraller rins and benar Registers |                                                                                                                                               |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIN                                                                                                                                                                        | FUNCTIONS SUPPORTED                                        | PRIORITY                                                                                                                                      |  |  |  |  |

| MODE         Internal/External reference         When using the serial interface, bit <ref> (register 0x6D, bit D4) controls this mode, if the MODE pin is tied low.</ref> |                                                            |                                                                                                                                               |  |  |  |  |

| DFS                                                                                                                                                                        | DATA FORMAT                                                | When using the serial interface, bit <df> (register 0x63, bit D3) controls this mode, ONLY if the DFS pin is tied low.</df>                   |  |  |  |  |

| DFS                                                                                                                                                                        | LVDS/CMOS                                                  | When using the serial interface, bit <odi> (register 0x6C, bits D3-D4) controls LVDS/CMOS selection independent of the state of DFS pin</odi> |  |  |  |  |

Figure 4. Simple Scheme to Configure Parallel Pins

## DESCRIPTION OF PARALLEL PINS

#### Table 3. SCLK Control Pin

| SCLK (Pin 29) | DESCRIPTION                                                           |

|---------------|-----------------------------------------------------------------------|

| 0             | LOW SPEED mode Disabled - Use for sampling frequencies above 50 MSPS. |

| DRVDD         | LOW SPEED mode Enabled - Use for sampling frequencies below 50 MSPS.  |

#### Table 4. SDATA Control Pin

| SDATA (Pin 28) | DESCRIPTION                                                                                                   |

|----------------|---------------------------------------------------------------------------------------------------------------|

| 0              | Normal operation (Default)                                                                                    |

| DRVDD          | STANDBY. This is a global power down, where ADC, internal references and the output buffers are powered down. |

#### Table 5. SEN Control Pin

| SEN (Pin 27) | DESCRIPTION                                                                                                   |

|--------------|---------------------------------------------------------------------------------------------------------------|

| 0            | CMOS mode: CLKOUT edge later by (3/12)Ts <sup>(1)</sup> ; LVDS mode: CLKOUT edge aligned with data transition |

| (1/3)DRVDD   | CMOS mode: CLKOUT edge later by (2/12)Ts ; LVDS mode: CLKOUT edge aligned with data transition                |

| (2/3)DRVDD   | CMOS mode: CLKOUT edge later by (1/12)Ts ; LVDS mode: CLKOUT edge earlier by (1/12)Ts                         |

| DRVDD        | Default CLKOUT position                                                                                       |

(1) Ts = 1/Sampling Frequency

#### Table 6. DFS Control Pin

| DFS (Pin 6) | DESCRIPTION                                       |

|-------------|---------------------------------------------------|

| 0           | 2's complement data and DDR LVDS output (Default) |

| (1/3)DRVDD  | 2's complement data and parallel CMOS output      |

| (2/3)DRVDD  | Offset binary data and parallel CMOS output       |

| DRVDD       | Offset binary data and DDR LVDS output            |

#### Table 7. MODE Control Pin

| MODE (Pin 23) | DESCRIPTION        |

|---------------|--------------------|

| 0             | Internal reference |

| (1/3)AVDD     | External reference |

| (2/3)AVDD     | External reference |

| AVDD          | Internal reference |

## SERIAL INTERFACE

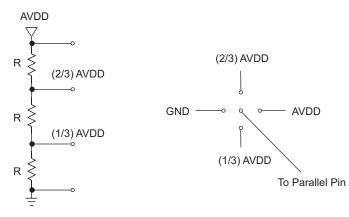

The ADC has a set of internal registers, which can be accessed through the serial interface formed by pins SEN (Serial interface Enable), SCLK (Serial Interface Clock), SDATA (Serial Interface Data) and RESET. After device power-up, the internal registers must be reset to their default values by applying a high-going pulse on RESET (of width greater than 10 ns).

Serial shift of bits into the device is enabled when SEN is low. Serial data SDATA is latched at every falling edge of SCLK when SEN is active (low). The serial data is loaded into the register at every 16th SCLK falling edge when SEN is low. If the word length exceeds a multiple of 16 bits, the excess bits are ignored. Data is loaded in multiples of 16-bit words within a single active SEN pulse.

The first 8 bits form the register address and the remaining 8 bits form the register data. The interface can work with SCLK frequency from 20 MHz down to very low speeds (few Hertz) and also with non-50% SCLK duty cycle.

Copyright © 2007, Texas Instruments Incorporated

## TEXAS INSTRUMENTS www.ti.com

# **REGISTER INITIALIZATION**

After power-up, the internal registers *must* be reset to their default values. This is done in one of two ways:

1. Either through hardware reset by applying a high-going pulse on RESET pin (of width greater than 10 ns) as shown in Figure 5.

OR

2. By applying software reset. Using the serial interface, set the <RST> bit (D1 in register 0x6C) to **high**. This initializes the internal registers to their default values and then self-resets the <RST> bit to **low**. In this case the RESET pin is kept **low**.

# SERIAL INTERFACE TIMING CHARACTERISTICS

Typical values at 25°C, min and max values across the full temperature range  $T_{MIN} = -40^{\circ}C$  to  $T_{MAX} = 85^{\circ}C$ , AVDD = DRVDD = 3.3 V (unless otherwise noted)

|                     |                        | MIN  | TYP | MAX | UNIT |

|---------------------|------------------------|------|-----|-----|------|

| f <sub>SCLK</sub>   | SCLK frequency         | > DC |     | 20  | MHz  |

| t <sub>SLOADS</sub> | SEN to SCLK setup time |      | 25  |     | ns   |

| t <sub>SLOADH</sub> | SCLK to SEN hold time  |      | 25  |     | ns   |

| t <sub>DSU</sub>    | SDATA setup time       |      | 25  |     | ns   |

| t <sub>DH</sub>     | SDATA hold time        |      | 25  |     | ns   |

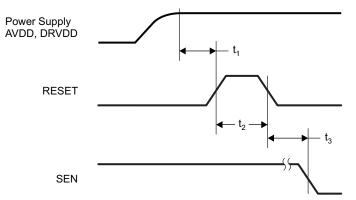

## **RESET TIMING**

Typical values at 25°C, min and max values across the full temperature range  $T_{MIN} = -40^{\circ}C$  to  $T_{MAX} = 85^{\circ}C$ , AVDD = DRVDD = 3.3 V (unless otherwise noted)

|                 | PARAMETER            | TEST CONDITIONS                                             | MIN | TYP | MAX | UNIT |

|-----------------|----------------------|-------------------------------------------------------------|-----|-----|-----|------|

| t <sub>1</sub>  | Power-on delay       | Delay from power-up of AVDD and DRVDD to RESET pulse active | 5   |     |     | ms   |

| t <sub>2</sub>  | Reset pulse width    | Pulse width of active RESET signal                          | 10  |     |     | ns   |

| t <sub>3</sub>  | Register write delay | Delay from RESET disable to SEN active                      | 25  |     |     | ns   |

| t <sub>PO</sub> | Power-up time        | Delay from power-up of AVDD and DRVDD to output stable      |     | 6.5 |     | ms   |

NOTE: A high-going pulse on RESET pin is required in serial interface mode in case of initialization through hardware reset. For parallel interface operation, RESET has to be tied permanently HIGH.

Figure 6. Reset Timing Diagram

# SERIAL REGISTER MAP

Table 8 gives a summary of all the modes that can be programmed through the serial interface.

| REGISTER<br>ADDRESS<br>IN HEX |                                                                        | REGISTER FUNCTIONS                     |                                                                                                      |                                                                                               |                                                                          |          |                                             |         |  |  |  |

|-------------------------------|------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------|---------------------------------------------|---------|--|--|--|

| A7 – A0                       | D7                                                                     | D6                                     | D5                                                                                                   | D4                                                                                            | D3                                                                       | D2       | D1                                          | D0      |  |  |  |

| 62                            |                                                                        | OUTPU<br>POSI                          | POSN><br>IT DATA<br>ITION<br>MMABILITY                                                               | <clkout posn=""><br/>OUTPUT CLOCK POSITION PROGRAMMABILITY</clkout>                           |                                                                          |          |                                             |         |  |  |  |

| 63                            | <b><stby></stby></b><br>GLOBAL<br>POWER<br>DOWN                        |                                        |                                                                                                      | <low speed=""><br/>ENABLE LOW<br/>SAMPLING<br/>FREQUENCY<br/>OPERATION</low>                  | <df><br/>DATA FORMAT -<br/>2's COMP or<br/>STRAIGHT<br/>BINARY</df>      |          |                                             |         |  |  |  |

| 65                            |                                                                        | <b>TERN&gt;</b> – ALL<br>AMP, CUSTO    |                                                                                                      |                                                                                               |                                                                          |          |                                             |         |  |  |  |

| 68                            |                                                                        |                                        |                                                                                                      |                                                                                               | <gain> GAIN PR</gain>                                                    | OGRAMM   | 1ING <gain> - 1 dB</gain>                   | to 6 dB |  |  |  |

| 69                            |                                                                        |                                        | <cus< td=""><td>STOM A&gt; CUSTOM</td><td>PATTERN (D7 TO I</td><td>D0)</td><td></td><td></td></cus<> | STOM A> CUSTOM                                                                                | PATTERN (D7 TO I                                                         | D0)      |                                             |         |  |  |  |

| 6A                            |                                                                        |                                        |                                                                                                      | <custom< td=""><td>B&gt; CUSTOM PATTE</td><td>ERN (D13</td><td>TO D8)</td><td></td></custom<> | B> CUSTOM PATTE                                                          | ERN (D13 | TO D8)                                      |         |  |  |  |

| 6B                            |                                                                        |                                        | <(                                                                                                   | CLKIN GAIN> INPU                                                                              | T CLOCK BUFFER                                                           | GAIN PRO | OGRAMMABILITY                               |         |  |  |  |

| 6C                            |                                                                        |                                        |                                                                                                      |                                                                                               | <pre><odi> OUTPUT DATA INTERFACE - DDR LVDS or PARALLEL CMOS</odi></pre> |          |                                             |         |  |  |  |

| 6D                            | <scaling> POWER SCALING</scaling>                                      |                                        |                                                                                                      | <b>REF&gt;</b> INTERNAL or EXTERNAL REFERENCE                                                 |                                                                          |          |                                             |         |  |  |  |

| 7E                            | <b><data term=""></data></b><br>INTERNAL TERMINATION – DATA<br>OUTPUTS |                                        |                                                                                                      |                                                                                               | Kout Term><br>Ination – Output                                           | CLOCK    | <b>LVDS CUR</b><br>LVDS CURRE<br>PROGRAMMAE | ENT     |  |  |  |

| 7F                            | LVDS C                                                                 | CURR DOUBLE><br>LVDS CURRENT<br>DOUBLE |                                                                                                      |                                                                                               |                                                                          |          |                                             |         |  |  |  |

# Table 8. Summary of Functions Supported by Serial Interface <sup>(1)(2)</sup>

(1) The unused bits in each register (shown by blank cells in above table) must be programmed as '0'.

(2) Multiple functions in a register can be programmed in a single write operation.

# DESCRIPTION OF SERIAL REGISTERS

Each register function is explained in detail below.

| Table 9. Serial Register A |                                                                                                                           |                                                                                                                                           |                               |               |                |                                 |         |    |  |  |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------|----------------|---------------------------------|---------|----|--|--|

| A7 – A0 (hex)              | D7                                                                                                                        | D6                                                                                                                                        | D5                            | D4            | D3             | D2                              | D1      | D0 |  |  |

| 62                         |                                                                                                                           | <data posn=""><br/>OUTPUT DATA<br/>POSITION<br/>PROGRAMMABILITY<clkout posn=""><br/>OUTPUT CLOCK POSITION PROGRAMMABILITY</clkout></data> |                               |               |                |                                 |         |    |  |  |

| D4 — D0                    | <c< td=""><td></td><th>SN&gt; Output</th><td>clock pos</td><td>ition progra</td><td>mmability</td><td></td><td></td></c<> |                                                                                                                                           | SN> Output                    | clock pos     | ition progra   | mmability                       |         |    |  |  |

| 00001                      |                                                                                                                           | fault CLKOU<br>sition are spe                                                                                                             | •                             |               |                | nings with this<br>able.        | s clock |    |  |  |

| XX011                      | CN                                                                                                                        | <b>IOS</b> – Falling                                                                                                                      | edge later                    | by (1/12) T   | S              |                                 |         |    |  |  |

|                            | LV                                                                                                                        | <b>DS</b> – Falling                                                                                                                       | edge earlie                   | r by (1/12)   | Ts             |                                 |         |    |  |  |

| XX101                      | CN                                                                                                                        | <b>IOS</b> – Falling                                                                                                                      | edge later                    | by (3/12) T   | S              |                                 |         |    |  |  |

|                            | LV                                                                                                                        | <b>DS</b> – Falling                                                                                                                       | edge aligne                   | ed with data  | transition     |                                 |         |    |  |  |

| XX111                      | CN                                                                                                                        | <b>IOS</b> – Falling                                                                                                                      | edge later                    | by (2/12) T   | s              |                                 |         |    |  |  |

|                            | LV                                                                                                                        | <b>DS</b> – Falling                                                                                                                       | edge aligne                   | ed with data  | transition     |                                 |         |    |  |  |

| 01XX1                      | CN                                                                                                                        | IOS – Rising                                                                                                                              | edge later                    | by (1/12) T   | 5              |                                 |         |    |  |  |

|                            | LV                                                                                                                        | <b>DS</b> – Rising                                                                                                                        | edge earlie                   | r by (1/12) T | ſs             |                                 |         |    |  |  |

| 10XX1                      | CN                                                                                                                        | <b>IOS</b> – Rising                                                                                                                       | edge later                    | by (3/12) T   | 5              |                                 |         |    |  |  |

|                            | LV                                                                                                                        | <b>DS</b> – Rising                                                                                                                        | edge aligne                   | ed with data  | transition     |                                 |         |    |  |  |

| 11XX1                      | CN                                                                                                                        | <b>IOS</b> – Rising                                                                                                                       | edge later                    | by (2/12) Ts  | 6              |                                 |         |    |  |  |

|                            | LV                                                                                                                        | <b>DS</b> – Rising                                                                                                                        | edge aligne                   | d with data   | transition     |                                 |         |    |  |  |

| D6 — D5                    |                                                                                                                           | ATA POSN><br>ogrammabili                                                                                                                  |                               |               |                | a Position<br>n CMOS mod        | le)     |    |  |  |

| 00                         |                                                                                                                           | ings with this                                                                                                                            |                               |               |                | reset. Setup/l<br>ming characte |         |    |  |  |

| 01                         | Da                                                                                                                        | ta Position 2                                                                                                                             | <ul> <li>Setup tim</li> </ul> | ne increases  | s by (2/36) Ts | 6                               |         |    |  |  |

| 10                         | Da                                                                                                                        | ta Position 3                                                                                                                             | <ul> <li>Setup tim</li> </ul> | ne increases  | s by (5/36) Ts | 6                               |         |    |  |  |

| 11                         | Da                                                                                                                        | ta Position 4                                                                                                                             | - Setup tim                   | ne decrease   | s by (6/36) T  | S                               |         |    |  |  |

#### SLWS203-DECEMBER 2007

### Table 10. Serial Register B

| A7 – A0 (hex) | D7                                              | D6 | D5 | D4                                                                           | D3                                                                      | D2 | D1 | D0 |

|---------------|-------------------------------------------------|----|----|------------------------------------------------------------------------------|-------------------------------------------------------------------------|----|----|----|

| 63            | <b><stby></stby></b><br>GLOBAL<br>POWER<br>DOWN |    |    | <low speed=""><br/>ENABLE LOW<br/>SAMPLING<br/>FREQUENCY<br/>OPERATION</low> | <b><df></df></b><br>DATA<br>FORMAT<br>2's COMP or<br>STRAIGHT<br>BINARY |    |    |    |

| D3 | <df> Output data format</df>                                             |

|----|--------------------------------------------------------------------------|

| 0  | 2's complement                                                           |

| 1  | Straight binary                                                          |

| D4 | <low speed=""> Low sampling frequency operation</low>                    |

| 0  | Default SPEED mode for 50 < Fs ≤ 200 MSPS                                |

| 1  | Low SPEED mode $1 \le Fs \le 50$ MSPS                                    |

| D7 | <stby> Global power down</stby>                                          |

| 0  | Normal operation                                                         |

| 1  | Global power down (includes ADC, internal references and output buffers) |

# Table 11. Serial Register C

| A7 – A0 (hex) | D7                                                 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---------------|----------------------------------------------------|----|----|----|----|----|----|----|

| 65            | <b><test b="" patte<=""><br/>TOGGLE, RA</test></b> |    |    |    |    |    |    |    |

| D7 — D5 | <test pattern=""> Outputs selected test pattern on data lines</test>                 |

|---------|--------------------------------------------------------------------------------------|

| 000     | Normal operation                                                                     |

| 001     | All 0s                                                                               |

| 010     | All 1s                                                                               |

| 011     | Toggle pattern – alternate 1s and 0s on each data output and across data outputs     |

| 100     | Ramp pattern – Output data ramps from 0x0000 to 0x3FFF by one code every clock cycle |

| 101     | Custom pattern – Outputs the custom pattern in CUSTOM PATTERN registers A and B      |

| 111     | Unused                                                                               |

SLWS203-DECEMBER 2007

## Table 12. Serial Register D

| A7 – A0 (hex) | D7 | D6 | D5 | D4 | D3                                                          | D2 | D1 | D0 |

|---------------|----|----|----|----|-------------------------------------------------------------|----|----|----|

| 68            |    |    |    |    | <gain> GAIN PROGRAMMING <gain> - 1 dB to 6 dB</gain></gain> |    |    |    |

| D3 — D0 | <gain> Gain programmability</gain> |

|---------|------------------------------------|

| 1000    | 0 dB gain, default after reset     |

| 1001    | 1 dB                               |

| 1010    | 2 dB                               |

| 1011    | 3 dB                               |

| 1100    | 4 dB                               |

| 1101    | 5 dB                               |

| 1110    | 6 dB                               |

## Table 13. Serial Register E

| A7 – A0 (hex) | D7 | D6                                                 | D5 | D4 | D3 | D2 | D1 | D0 |  |

|---------------|----|----------------------------------------------------|----|----|----|----|----|----|--|

| 69            |    | <custo< td=""><td></td><td></td><td></td></custo<> |    |    |    |    |    |    |  |

| 6A            |    | <b>CUSTOM B&gt;</b> CUSTOM PATTERN (D10 TO D5)     |    |    |    |    |    |    |  |

| Reg 69 | D7 — D3 | Program bits D4 to D0 of custom pattern  |

|--------|---------|------------------------------------------|

| Reg 6A | D5 — D0 | Program bits D10 to D5 of custom pattern |

### Table 14. Serial Register F

| A7 – A0 (hex) | D7 | D6 | D5                                                              | D4 | D3 | D2 | D1 | D0 |

|---------------|----|----|-----------------------------------------------------------------|----|----|----|----|----|

| 6B            |    |    | <clkin gain=""> INPUT CLOCK BUFFER GAIN PROGRAMMABILITY</clkin> |    |    |    |    |    |

| 110010 | Gain 4, maximum gain       |

|--------|----------------------------|

| 101010 | Gain 3                     |

| 100110 | Gain 2                     |

| 100000 | Gain1, default after reset |

| 100011 | Gain 0 minimum gain        |

#### SLWS203-DECEMBER 2007

## Table 15. Serial Register G

| A7 – A0 (hex) | D7 | D6 | D5 | D4        | D3                                      | D2 | D1                                    | D0 |